Microwatt Momentum

OpenPOWER HW Design Hackathon

Microwatt Momentum

OpenPOWER HW Design Hackathon

Microwatt Momentum Challenge 2025

The Microwatt Momentum Challenge is a premier hardware hackathon fostering innovation around the open-source Microwatt POWER CPU core. Our goal is to accelerate the creation of novel and reproducible hardware peripherals and system-level solutions using open-source tools and platforms.

Submitted Proposals

Accepted Proposals

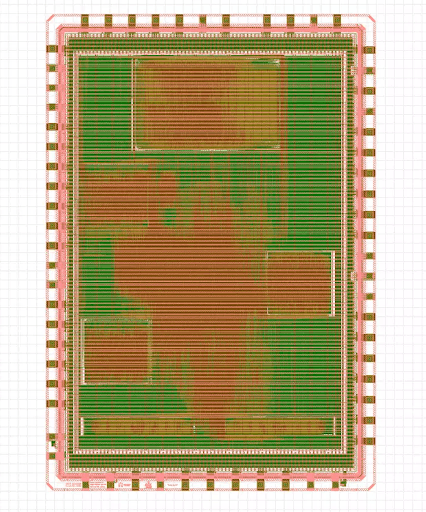

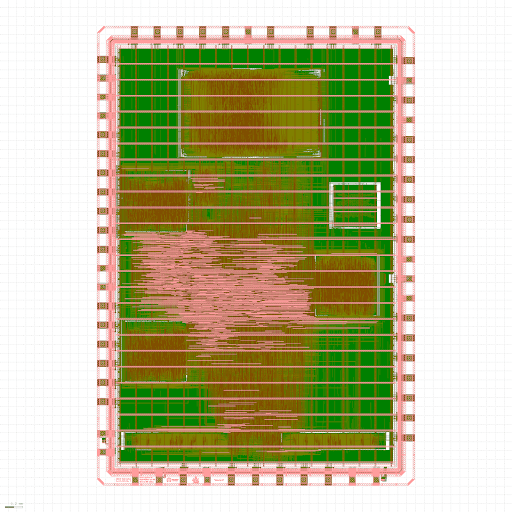

Winning Designs Fabricated

The latest Microwatt Momentum Challenge saw an impressive field of submissions, pushing the boundaries of open-source POWER architecture. We are thrilled to announce the winning designs that will be fabricated by ChipFoundry and delivered as packaged parts to their respective teams.

Eleftherios Batzolis (Design Lead & Architect)

Repository: https://github.com/Lefteris-B/microwatt_design_challenge (main branch - taped out)

Kushal (System Integration), Aditya A (Hardware Debug Block Design), Adhitya S (Verification & Testbenches), Ahan (Peripheral Design), Syed Abubakr (Firmware Development)

Repository: https://github.com/blue67chillout/Microwatt-Based-MInimalx-Debugger.git

Sameer Srivastava (OpenFPGA Integration Lead), Ketan (Microwatt Wrapper & Interfaces), Shikha (Verification), Ira Tyagi (Documentation & Report)

Mentor: Dr. Anand Kumar Singh

Repository: https://github.com/s-m33r/chipfoundry_fpga_test

Challenge Details

Unleash the Power of Open-Source Hardware!

Welcome to Microwatt Momentum, a hackathon designed to spark innovation and collaboration within the OpenPOWER ecosystem. This event challenges hardware developers to push the boundaries of what's possible with Microwatt, the open-source POWER CPU core.

The hackathon aims to bring together bright minds to explore Microwatt's potential and contribute to the growing open-source hardware movement.

Theme & Challenge: "Microwatt for the open computing era"

Participants are challenged to develop creative and impactful applications that leverage the Microwatt CPU core. Your project should demonstrate a useful and effective way of integrating the Microwatt POWER CPU core.

Target Audience & Eligibility

This hackathon is open to:

Hardware Engineers & FPGA Developers

Software Developers

Students & Researchers

Anyone with a passion for open-source hardware and a desire to innovate

Projects can span various use cases but must deliver working, repeatable solutions. Example projects include designing a custom hardware accelerator for sensor data processing or integrating Microwatt with novel sensing technologies.

Key Technologies & Platforms

Participants are expected to utilize:

Microwatt CPU Core

OpenPOWER ISA

FPGA Simulation/Synthesis Tools (e.g., GHDL, Yosys, Verilator, NextPNR)

Software and Dev Toolchains (e.g., GCC for POWER, GDB)

Optional: Access to actual POWER hardware or FPGA boards and various sensor types

ChipFoundry OpenFrame SoC platform

How to Enter

Login to your Github account and create a public GitHub repository using this template repo.

Commit a Readme file with the project description and proposal.

Submit the URL for your Github repo using the form below on or before Sep 22, 2025 (by 11:59pm PST).

If selected for the final round, you will be notified by email. Update your Github repo with your final design on or before Oct 31, 2025.

Limit one entry per person, per email address. The entry must be original and use an approved open-source license. All designs must be implemented and fit in the Openframe User Project area.

View the Recording from Webinar 1

Please find the link to the video recording.

You can also find a link to the slides here.

View the Recording from Webinar 2

Please find the link to the video recording.

Slides are here.

Project Requirements

All requirements must be met to be eligible to win.

All submission content, documentation, prompt must be in English

A short description of the project must be included with your design.

All designs must be implemented and fit in the OpenFrame User Project area.

The VHDL/Verilog for the design can be coded by AI.

Testbenches for RTL verification must be provided as a reproducible element of this process. Constraints for STA and SDF simulations must also be provided.

If AI was used for any of the design process. all prompts or GPT session logs used in the design must be provided as part of the deliverables for the design.

The design needs to be open source with all materials required to reproduce made public. The project must include an official open-source license (e.g. Apache2, MIT, etc.)

To facilitate reproducibility by the community, we recommend the design be implemented using the OpenLane chipIgnite flow including all configuration and run results. However, we will accept any open-source implementation flow provided it is documented and reproducible.

Must be implementable in SKY130 with available standard cells.

The design must pass precheck and tapeout submissions on the ChipFoundry platform.

Winners must provide a video and screenshots demonstrating the creation of the project in a how-to or step-by-step format. The images and link to the video must be included in the documentation for their project in the GitHub repo. These materials may be used by ChipFoundry for promotional purposes.

Judging Criteria

Projects will be evaluated by a panel of experts based on the following criteria:

Project Documentation: The ability to easily replicate the project.

Prompt Documentation: Documentation of AI LLM prompts used, if applicable.

Code Quality: Coding best practices, documentation, and use of modular design.

Verification Coverage: The thoroughness of Verilog/VHDL test benches and post-PAR/cell placement analysis.

Design Technical Merit: The originality and improvement the new design brings to the existing processor.

All requirements must be met to be eligible to win, including providing a video and screenshots demonstrating the project's creation.

Judges

Mohamed Kassem - ChipFoundry

Peter Hofstee - IBM

Tim Pearson - Raptor Computing Systems

Paul Mackerras - IBM retired

Program Timeline

Registration Opens: September 2, 2025

Webinar 1: September 10, 2025 ( join )

Project Proposal Submission Deadline: September 22, 2025 (by 11:59pm PST)

Webinar 2: September 24, 2025

Final Design Submission: November 3, 2025 (by 11:59pm PST)

Final design selection: November 4-7, 2025

Winner Announcement: November 8, 2025

The Prize

The top three winning designs will be fabricated by ChipFoundry and delivered to their respective design teams in the form of a packaged part.

Resources

Participants will have access to:

Microwatt GitHub Repository: Official source code, documentation, and examples.

OpenPOWER Foundation Website: General information about the OpenPOWER ISA and community.

Community Forums/Chat: Dedicated channels for questions, collaboration, and mentor support.

chipIgnite Resources: Information and guidelines for preparing designs for the process on SkyWater 130nm. (Link to be provided upon registration for relevant teams).

We use cookies to improve user experience. Choose what cookie categories you allow us to use. You can read more about our Cookie Policy by clicking on Cookie Policy below.

These cookies enable strictly necessary cookies for security, language support and verification of identity. These cookies can’t be disabled.

These cookies collect data to remember choices users make to improve and give a better user experience. Disabling can cause some parts of the site to not work properly.

These cookies help us to understand how visitors interact with our website, help us measure and analyze traffic to improve our service.

These cookies help us to better deliver marketing content and customized ads.